However, I think I can elucidate the issue for you anyway.

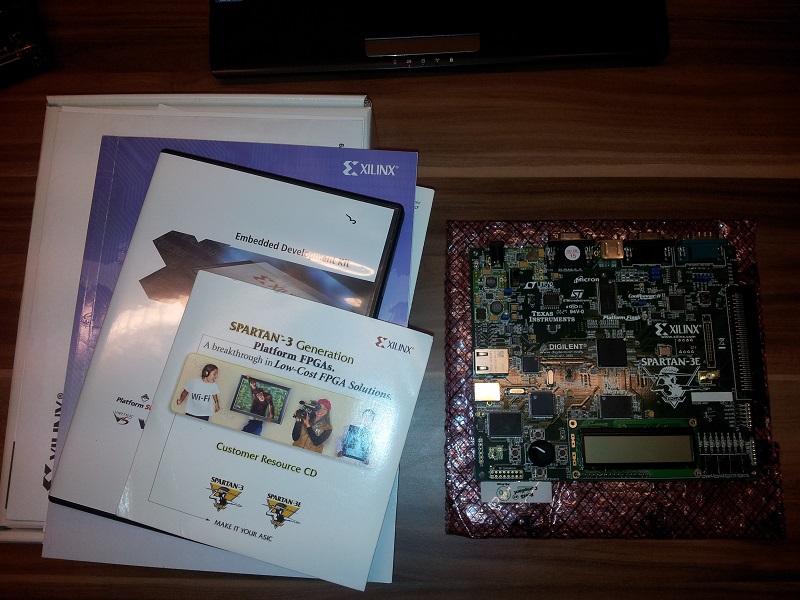

FPGA SIMULATION FOR SPARTAN 3E CODE

I'm assuming that you left some code out of your first example since that shouldn't even compile. Solution ( assuming original functionality is correct): reg flop_sel įlop_sel <= sel // Non-blocking assignment !!!Īlways (flop_sel) reg2 = func1(x,y,z) // Blocking assignment !!! If (sel) reg2 <= func1(x,y,z) // Non-blocking assignment !!! Solution ( assuming original functionality is wrong): always clk) Solution: assign wire1 = sel ? func1(x,y,z) : func2(a,b,c) Solution: always // <- IEEE Std 1364-2001 constructĬombinational logic on wire: always (sel) force wire1 = func1(x,y,z) Misuse of procedural continuous assignment and solutions:Ĭombinational logic on reg: always (sel) assign reg1 = func1(x,y,z) Alternative approaches are more reliable. In generate using procedural continuous assignment (with force/ release) should only be used if absolutely necessary. Use force/ release if procedural continuous assignment as needed. IEEE Std 1800-2005 § 25.3, IEEE Std 1800-2009 § C.4.2 and IEEE Std 1800-2012 § C.4.2 recognizes assign used this way causes confusion and is the source of errors. Using assign/ deassign in this manner is being considered to be depreciated in future IEEE 1800 release.

/i/02868/products/2019-02-22T06%3A46%3A58.641Z-IMG_20190214_030742.jpg)

OR (currently valid but discouraged) // translate_off The release/ deassign allows the the register/wire to be assigned in the usual manner.

It is the one case procedural continuous assignment are allowed in RTL when used with the translate off keyword your synthesizer. This is a well documented issue with Verilog. q should go to 1 the the asynchronous set is still enabled, but nothing to trigger in in the sensitivity list. In simulation however the model is inaccurate if rst_n and set_n are both low then rst_n goes high. It will synthesize to a flop with an asynchronous set and reset with priority to reset. always clk) assign data_in = Data is functional the same as: always clk)Ī valid use of procedural continuous assignment would be should be applited to the following: always clk or negedge rst_n, negedge set_n) begin.always assign data_in = Data is functional the same as always data_in = Data.However it is recommend to limit the use to behavior modeling of an analog block, test bench files, or fixing RTLgate functional mismatches. Procedural continuous assignments are synthesizable, by most tools. It has been part of the LRM since 1364-1995. force can be applied to registers and nets (i.e. assign can be applied to register types such as reg, integer, and real. A new continuous assignment process is created when the line is reached in the procedural block. It is the use of an assign or force (and their corresponding counterparts deassign and release) within procedural block. Please contact us for projects at: Nepal also have create Reference Guide on VHDL Programming, Verilog Programming, Tcl Programming, the detail of the reference guide is also available on below.It is called procedural continuous assignment. We have published paper on Very High Speed Packet Processing, PCIe 4.0 Terminologies, Image Processing with Zynq FPGA, UART Implementation on FPGA etc.ĭigitronix Nepal has Created 5 Courses on FPGA Design with High Level Synthesis (HLS: C/C++ Design Approach on FPGA Design), VHDL Programming, Verilog Programming, Embedded system design with xilinx Zynq FPGA and VIVADO.įor $10 Course Coupon of our courses, please send us email at: Nepal can provide FPGA Design, Research and Development Services and ASIC/VLSI Design and Verification. We have done FPGA Design projects for Image Processing, Image Annotation, High Speed Data Transfer Application. We are working in this field from past 4+ years. Udemy Courses from Digitronix Nepal and LogicTronix: Our CoursesįPGA Research and Development in Nepal: 24th April, 2018.ĭigitronix Nepal has expertise on FPGA Design, IP Design and Verification.

0 kommentar(er)

0 kommentar(er)